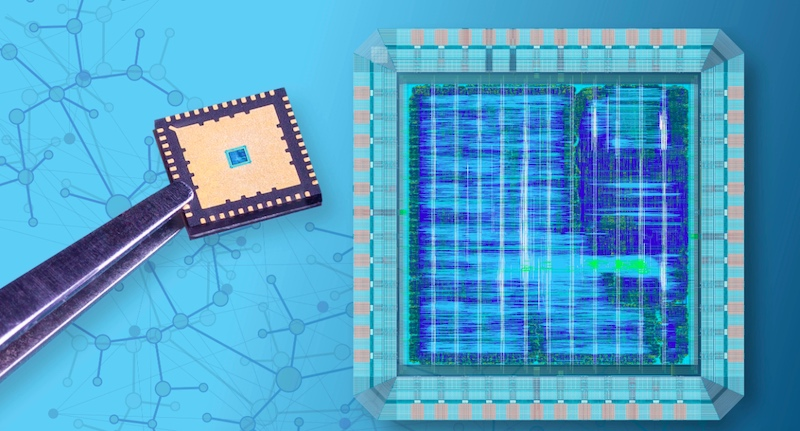

Un equipo de investigación de ETH Zurich aprovecha los circuitos de aprendizaje basados en picos existentes para proponer una arquitectura biológicamente plausible que tiene un gran éxito en la clasificación de patrones de picos espacio-temporales distintos y complejos. El trabajo contribuye al diseño de sistemas de procesamiento neuromórfico de señal mixta de potencia ultrabaja capaces de distinguir patrones espacio-temporales en la actividad de picos.

(Synced)-Spiking Neural Networks (SNN) representa la tercera generación de redes neuronales artificiales. Los modelos SNN se construyen utilizando aspectos espaciales y temporales de los datos de entrada y, como tal, avanzan un paso más hacia el verdadero procesamiento inspirado en el cerebro. Los SNN han demostrado ser muy prometedores y potenciales en plataformas de hardware de procesamiento sensorial y de computación de borde de baja potencia.

En el artículo An Error-Propagation Spiking Neural Network Compatible With Neuromorphic Processors , los investigadores de ETH Zurich aprovechan los circuitos de aprendizaje basados en picos existentes para proponer una arquitectura biológicamente plausible que tiene un gran éxito en la clasificación de distintos patrones de picos espacio-temporales complejos.

El estudio avanza en el diseño y desarrollo de sistemas de procesamiento neuromórfico de señal mixta de potencia ultrabaja capaces de distinguir patrones espacio-temporales en la actividad de picos producida, por ejemplo, por sensores de visión o auditivos. Los investigadores dicen que el bajo consumo de energía del hardware de la red (las neuronas solo transmiten información cuando los datos de entrada alcanzan un umbral elevado) hace que los SNN sean buenos candidatos para el procesamiento de señales biológicas y las interfaces cerebro-máquina.

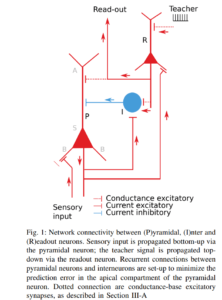

Los investigadores describen primero la topología de red de un modelo cortical. Inspirado por la funcionalidad, la conectividad y la diversidad de tipos de células en la neocorteza humana, el diseño del modelo cortical comprende tanto neuronas excitadoras multicompartimentales basadas en la frecuencia como interneuronas inhibidoras.

La neurona multicompartimental se esquematiza como una neurona piramidal de tres compartimentos (apical, basal y somática) (P). Esta neurona piramidal se utiliza para integrar información sensorial ascendente y una señal de enseñanza descendente, y su compartimento apical recibe retroalimentación de áreas de orden superior, así como de las interneuronas.

Durante el proceso de aprendizaje de las neuronas, las interneuronas son impulsadas lateralmente por las neuronas piramidales, que aprenden a replicar la actividad de picos de neuronas específicas en la capa superior, por ejemplo, para cancelar la señal del profesor de arriba hacia abajo en el compartimento apical de la neurona piramidal. De manera similar, la velocidad de disparo de la neurona de lectura (R) tenderá a la señal del maestro (que proviene de la capa superior con la conectividad lateral que proviene de las interneuronas).

Luego, los investigadores adaptan el modelo para permitir que se implemente directamente con circuitos neuromórficos por debajo del umbral mediante el uso de ecuaciones y mecanismos de plasticidad. Diseñan una regla de aprendizaje para conexiones ascendentes, donde las actualizaciones de peso incrementales se basan en la diferencia entre las corrientes de membrana somática y basal. El equipo explica que un término de histéresis en la ecuación da lugar a una región de parada de aprendizaje, que permite el aprendizaje permanente.

Siguiendo el modelo basado en tasas propuesto por J. Sacramento et al. [2018], el equipo evaluó la red de picos propuesta en tareas de discriminación y reconocimiento de patrones espacio-temporales.

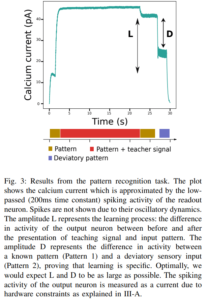

En la tarea de reconocimiento de patrones, la diferencia de actividad entre un Patrón 1 conocido y una entrada sensorial desviada (Patrón 2) demostró que el aprendizaje del método propuesto es específico. En la tarea de discriminación de patrones, la actividad de picos de las neuronas de salida clasificó correctamente los patrones de entrada.

La arquitectura propuesta se basa únicamente en actualizaciones de peso activadas por variables y parámetros locales y, por lo tanto, es adecuada para su implementación en chips neuromórficos analógicos / digitales de señal mixta. El estudio avanza en el desarrollo de chips de aprendizaje siempre activos de bajo consumo que se pueden aplicar en aplicaciones de computación periférica, robótica y computación distribuida.

El artículo Una red neuronal de propagación de errores compatible con procesadores neuromórficos está en arXiv .